# Superconducting optoelectronic loop neurons (1)

Cite as: J. Appl. Phys. 126, 044902 (2019); doi: 10.1063/1.5096403 Submitted: 17 March 2019 · Accepted: 20 June 2019 ·

Published Online: 25 July 2019

Jeffrey M. Shainline,<sup>1,a)</sup> 📵 Sonia M. Buckley,¹ Adam N. McCaughan,¹ Jeffrey T. Chiles,¹ Amir Jafari Salim,² Manuel Castellanos-Beltran, Christine A. Donnelly, Michael L. Schneider, Richard P. Mirin, and Sae Woo Nam

#### **AFFILIATIONS**

- <sup>1</sup>National Institute of Standards and Technology, 325 Broadway, Boulder, Colorado 80305, USA

- <sup>2</sup>HYPRES, Inc., 175 Clearbrook Rd., Elmsford, New York 10523, USA

#### **ABSTRACT**

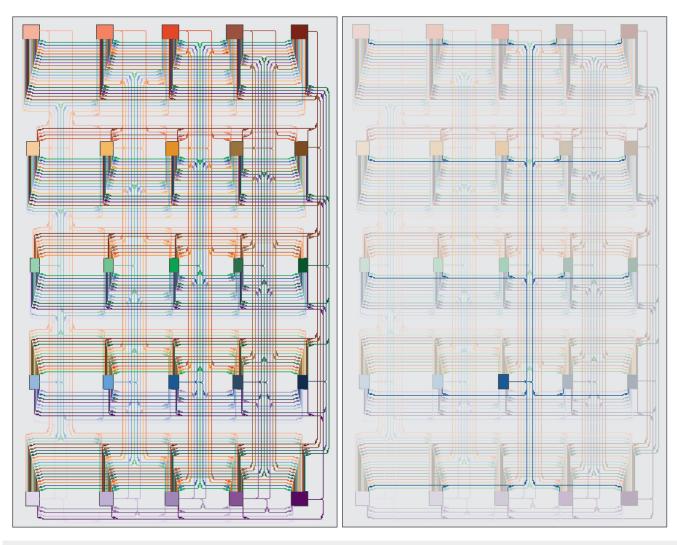

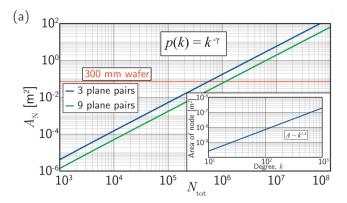

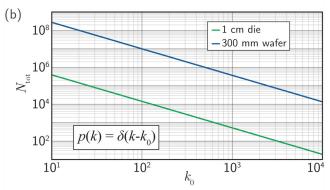

Superconducting optoelectronic hardware has been proposed for large-scale neural computing. In this work, we expand upon the circuit and network designs previously introduced. We investigate circuits using superconducting single-photon detectors and Josephson junctions to perform signal reception, synaptic weighting, and integration. Designs are presented for synapses and neurons that perform integration of rate-coded signals as well as detect coincidence events for temporal coding. A neuron with a single integration loop can receive input from thousands of synaptic connections, and many such loops can be employed for dendritic processing. We show that a synaptic weight can be modified via a superconducting flux-storage loop inductively coupled to the current bias of the synapse. Synapses with hundreds of stable states are designed. Spike-timing-dependent plasticity can be implemented using two photons to strengthen and two photons to weaken the synaptic weight via Hebbian-type learning rules. In addition to the synaptic receiver and plasticity circuits, we describe an amplifier chain that converts the current pulse generated when a neuron reaches threshold to a voltage pulse sufficient to produce light from a semiconductor diode. This light is the signal used to communicate between neurons in the network. We analyze the performance of the elements in the amplifier chain to calculate the energy consumption per photon created. The speed of the amplification sequence allows neuronal firing up to at least 20 MHz, independent of connectivity. We consider these neurons in network configurations to investigate near-term technological potential and long-term physical limitations. By modeling the physical size of superconducting optoelectronic neurons, we calculate the area of these networks. A system with 8100 neurons and 330 430 total synapses will fit on a  $1 \times 1$  cm<sup>2</sup> die. Systems of millions of neurons with hundreds of millions of synapses will fit on a 300 mm wafer. For multiwafer assemblies, communication at light speed enables a neuronal pool the size of a large data center (105 m2) comprised of trillions of neurons with coherent oscillations at 1 MHz.

© 2019 Author(s). All article content, except where otherwise noted, is licensed under a Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/). https://doi.org/10.1063/1.5096403

## I. INTRODUCTION

Complete understanding of the information processing underlying cognition remains a significant scientific challenge. Progress in neuroscience, computer science, psychology, and neural engineering makes this a fruitful time for elucidation of intelligence. Biological experiments and software simulations would be greatly augmented by artificial hardware with complexity comparable to systems we know to be conscious. Intelligent systems implemented with hardware optimized for neural computing may inform us regarding the limits of cognition imposed by the speed of light while providing technological opportunities sufficient to spawn a new domain in the computing industry.

Neural computing appears uniquely capable of the distributed, yet integrated, information processing that characterizes intelligent systems. Many approaches to neural computing are being developed, and the maturity of the semicondutor industry makes CMOS a wise initial platform. Yet, the central role of communication in neural computing indicates that hardware incorporating different physics may be advantageous for this application. In previous work, we considered the potential for superconducting optoelectronic hardware to perform neural operations. The principal assumption guiding the design of the hardware platform is that photons are the entities best suited for communication in large-scale neural systems. The hardware platform leverages optical communication over short and long distances to enable dense local fan-out as well as distant communication with the shortest possible delay. In this work, we present details of the design of superconducting optoelectronic neurons and networks

a)Electronic mail: jeffrey.shainline@nist.gov

that appear capable of achieving the functions required for cognitive computing.

This work expands upon the initial concepts presented in Ref. 1 in several ways. Most importantly, we introduce circuits that utilize light for communication between neurons but set synaptic weights in the electronic domain, thereby efficiently utilizing photons and enabling complex, event-based plasticity mechanisms. In Ref. 1, the proposed neural circuits were based on arrays of single-photon detectors (SPDs) in series or in parallel, and it was assumed that synaptic weights would be accomplished by varying the number of photons that reached the detector arrays. This approach to neuron design is inefficient because the production of photons dominates energy consumption in superconducting optoelectronic circuits, and more photons are generated than are used if the synaptic weight is established via variable attenuation in the photonic domain.

In the present work, we show that Josephson junctions (JJs) in conjunction with SPDs straightforwardly accomplish many neural operations and can be used to construct synapses that require a single photon for communication, with the synaptic weight set by the amount of electrical current generated during a photon-detection event. The simple SPD/JJ circuit investigated here transduces single-photon communication events to integrated supercurrent. We describe how to combine the signals of many such synapses in a shared integration loop using mutual inductors. We also discuss how to use these synapses to achieve inhibitory connections and dendritic processing. While the goal of photonic communication is to achieve high fan-out, in Ref. 1 fan-in was proposed to occur in the photonic domain. Here, we re-envision the dendritic tree and propose instead that a hierarchy of dendritic loops performs well for high fan-in. Regarding learning, we present techniques for controlling the synaptic weights, either through direct, electronic control for supervised training and machine learning or through correlated photon detection for spike-timing-dependent, short-term, homeostatic, and metaplasticity.

This work also goes beyond the initial concepts presented in Ref. 1 with the analysis of amplifier circuits capable of converting the current output from a JJ circuit to the voltage necessary to generate light from a semiconductor diode. Regarding scaling, this work builds on Ref. 1 with the consideration of networks characterized by graphs employed by cognitive systems. We analyze such networks to model spatial scaling and power consumption. We propose a routing architecture and consider the size of the computation and communication circuits in order to estimate network area and power density. We find that a network with  $1\times 10^6$  neurons and  $200\times 10^6$  synapses can fit on a 300 mm wafer and would dissipate less than 1 W of device power, illustrating the feasibility of cooling large-scale superconducting optoelectronic systems with conventional cryogenics. We conclude with the analysis of scaling limits due to the finite speed of light.

These refinements of superconducting optoelectronic network (SOEN) concepts have been summarized in a previous publication. The present work is a more thorough treatment of the subject, exploring the conceptual motivation of this work as well as many details of circuit concepts and simulations that were not included in Ref. 2. We begin with a summary of the neuroscientific principles that guide the design of this hardware platform.

#### A. General principles of cognitive systems

The foundational assumption of this work is that light is the physical entity best suited to achieve communication in cognitive neural systems. To motivate why light is essential for large-scale neural systems, we must describe the systems we intend to pursue.

Broadly speaking, we wish to pursue devices and networks capable of acquiring and assimilating information across a wide range of spatial, temporal, and categorical scales. In a neural cognitive system, spatial location within the network may correspond to information specific to content area or sensory modality, and spatial integration across the network corresponds to the integration across informational subjects and types. Information processing must occur across many levels of hierarchy with effective communication across local, regional, and global spatial scales, as well as temporal scales. These systems must continually place new information in context. It is required that a cognitive system maintain a slowly varying background representation of the world while transitioning between dynamical states under the influence of stimulus. The objective of this paper is to design general cognitive circuits with structural and dynamical attributes informed by neuroscience, network theory, and dynamical systems. Stated generally, systems combining functional specialization with functional integration are likely to perform well for many cognitive tasks.<sup>3</sup>

The theme of localized, differentiated processing combined with information integration<sup>5-11</sup> across space<sup>12,13</sup> and time<sup>14-18</sup> is central to the device and network designs we consider here. In the spatial domain, the demand for integration of information from many local areas requires not only dense local connectivity (as measured by a clustering coefficient<sup>19-21</sup>) but also connections between these local areas, which serve to combine the local information in a larger context at higher cognitive levels<sup>22</sup> (as measured by a short average path length<sup>23</sup>). High clustering combined with short average path length defines a small-world network.<sup>24</sup> For the highest performance, we expect this trend of integration of locally differentiated information to repeat across many scales in a nearly continuous manner 12 such that any node in the system is likely to be not only processing information with local neighbors but also receiving information from simpler, less-connected units, and transferring information to complex, highly connected units. Networks with this organization across scales are governed by power-law spatial scaling.

The patterns are related in the temporal domain where transient synchronized oscillations integrate information from various brain regions. <sup>14–16</sup> Information exchange can occur on very fast time scales, and results of these computations must be combined over longer times. The spatial structure of the network and its operation in the time domain are not independent. <sup>3,4,26</sup> Fast, local dynamics integrate information of closely related nodes through transient neuronal functional clusters, <sup>27</sup> while activity on slower scales can incorporate input from larger regions. <sup>28</sup> Networks with this organization in time are governed by a power-law frequency distribution, <sup>17,18,29</sup> characteristic of self-organized criticality. <sup>30</sup> Power-law spatial and temporal distributions underlie systems with fractal properties, <sup>18,29</sup> and self-similarity across space and time is advantageous for cognition. <sup>18,30–34</sup>

These conceptual arguments regarding information integration across spatial and temporal scales lead us to anticipate networks

utilizing hierarchical configuration, with processing on various scales being integrated at high levels to form a coherent cognitive state. The constitutive devices most capable of achieving these network functions are relaxation oscillators, the dynamical entities characterized by pulsing behavior the with resonant properties at many frequencies. Neurons are a subset of relaxation oscillators with complex operations adapted for spike-based computation. We return to relaxation oscillators shortly.

To illustrate how differentiated processing and information integration are implemented by neurons for cognition, consider vision.40 In early stages of visual processing, neurons located near each other in space will show similar tuning curves<sup>41</sup> in response to presented stimuli, thus forming locally coherent assemblies selecting for certain features of a visual scene. 16 These locally differentiated processing units are constructed from architectural motifs 42,43 and are manifest in biological hardware as minicolumns and columns,4which are dedicated to modeling a subset of sensory space. 45 To form a more complete representation of an object within a visual scene, or to make sense of a complex visual scene with many objects, the visual system must combine the information from many differentiated processors. This integration is accomplished with lateral connections between columns<sup>3</sup> as well as with feed-forward connections from earlier areas of visual cortex to later areas of visual cortex. 40 Such an architecture requires some of the neurons in any local region to have long-range projections, motivating the need for local connectivity for differentiated processing combined with distant connectivity for information integration across space.

To understand information integration in the time domain, consider synchronized oscillations at various frequencies in the context of the binding problem. 46,47 Stated as a question, the binding problem asks how the myriad stimuli presented to the brain can be quickly and continuously organized into a coherent cognitive moment. In the limited context of vision, we ask how a complex, dynamic visual scene can be structured into a discernible collection of objects that can be differentiated from each other and from an irrelevant background.48 Many studies provide evidence that fast, local oscillations are modulated by slower oscillations encompassing more neurons across a larger portion of the network. 14the case of columns in visual cortex, local clusters tuned to specific stimuli will form assemblies with transient synchronization at high frequencies ( $\gamma$  band, 20–80 Hz<sup>17</sup>). The information from many of these differentiated processors is integrated at higher levels of processing by synchronizing larger regions of neurons at lower frequencies ( $\alpha$  band, 1–5 Hz, and  $\theta$  band, 4–10 Hz<sup>17,28</sup>). The transient synchronization of neuronal assemblies is closely related to neuronal avalanches, 30,32 cascades of activity across many frequencies. Neuronal avalanches are observed in networks balanced at the critical point between order and chaos. 30-34 Self-similarity in the temporal domain implies operation at this critical point, 30,31,34 and operating at this phase transition is necessary to maximize the dynamic range of the network.<sup>32</sup> Inhibition and activity-based plasticity are crucial for achieving this balance. 17,18,51

Networks of excitatory principal neurons interspersed with inhibitory interneurons<sup>52</sup> with small-world characteristics naturally synchronize at frequencies determined by the circuit and network properties.<sup>18</sup> Slower frequency collective oscillations of networks of inhibitory interneurons provide short windows when certain

clusters of excitatory neurons are uninhibited and, therefore, susceptible to spiking.<sup>53</sup> This feedback through the inhibitory interneuron network provides a top-down means by which the dynamical state of the system can provide broad information to the local processing clusters. 16,50 Regions of cortex with higher information integration focus attention<sup>15</sup> on certain aspects of stimulus by opening receptive frequency windows at the resonant frequencies of relevant subprocessors, providing a mechanism by which binding occurs and background is ignored. 16,17,49,50 The result of this inhibitory structuring of time is a network with dynamic effective connectivity. 22,50 By constructing a network with a smallworld, power-law architecture from highly tunable relaxation oscillators and employing feedback through inhibitory oscillations, we produce a system that can change its effective structural and resonant properties very rapidly based on information gleaned from prior experiences of a large region of the network.<sup>17</sup>

This model of binding requires a means by which the resonant frequencies of neuronal assemblies can be associated with certain stimuli, and a means by which the inhibitory interneuron network can learn to associate different assemblies with different frequencies. Plastic synaptic weights make such adaptation possible. Synapses provide a means for the connectivity of the network to shape dynamics and functionality, and synapses adapt their states based on internal and external activities. As cortex evolves through dynamical states on various temporal and spatial scales, information stored in synapses is integrated across the network and used as a feedback to distributed subprocessors. <sup>16,50</sup>

For a cognitive system embedded in a dynamical environment to provide adaptive feedback as well as robust memory, the system must comprise a large number of synapses changing on different time scales due to different internal and external factors.<sup>54</sup> Synapses with many stable values of efficacy can significantly increase memory retention times,<sup>55</sup> and synapses that adapt not only their state of efficacy but also their probability of state transition are crucial for maximizing memory retention times.<sup>54,56</sup> Adaptation of probability of state transition is a mechanism of metaplasticity,<sup>5</sup> and many forms appear in biological systems. We expect a cognitive system to utilize differentiated regions of neurons, some with synapses changing readily between only two synaptic states, and other regions with synapses changing slowly between many distinguishable states. We further expect the network to update not only synaptic weights but also the probability of changing synaptic weights. The dynamical state of the system can then sample synaptic memory acquired at many times, in many contexts, while quickly adapting the dynamical trajectory as new stimulus is presented.

To summarize, cognition appears to require differentiated local processing combined with information integration across space, time, and experience. The structure of the network determines the dynamical state space, and the structure of the network adapts in response to stimulus and internal activity. We now ask the question: What physical systems are best equipped to perform these operations?

## B. Physics and hardware for cognition

The aforementioned insights from neuroscience lead us to emphasize several features of neural systems in hardware for cognition. First, we must use a physical signaling mechanism capable of achieving communication across networks with dense local clustering, midrange connectivity, and large-scale integration. Second, the relaxation oscillators that constitute the computational primitives of the system must perform many dynamical functions with a wide variety of time constants to enable and maximally utilize information processing through transient synchronized assemblies. Third, a variety of synapses must be achievable, ranging from binary to multistable. The strength of these synapses must adjust due to network activity, as must the update frequency.

#### 1. Optical communication

A principal challenge of differentiated computation with integrated information is communication. The core concept of the superconducting optoelectronic hardware platform is that light is excellent for this purpose. Light excels at communication for three reasons. First, light experiences no capacitance, resistance, or inductance, so dense, local clustering as well as long-range connections can be achieved without charge-based wiring parasitics. Second, it is possible to signal with single quanta of the electromagnetic field, thereby enabling the energy efficiency necessary for scaling. Third, light is the fastest entity in the universe. Short communication delays are ideal for maximizing the number of synchronized oscillations a neuron can participate in as well as the size of the neuronal pool participating in a synchronized oscillation. Light-speed communication, therefore, facilitates large networks with rich dynamics.

We have argued elsewhere that parasitics of electronic interconnects limit communication in neural systems. These limitations are ultimately due to the charge of the electron and its mass. Signals in the brain are transmitted via ionic conduction. The operating voltage of biological neurons is near 70 mV, so the energy penalty of  $CV^2/2$  is significantly reduced relative to semiconducting technologies operating at 1 V, and direct connections are possible. Yet, the low mobility of ions results in slow signal velocities, severely limiting the total size of biological neural systems.<sup>18</sup> Uncharged massless particles are better suited for communication in cognitive neural systems. Light is the natural candidate for this operation. It is possible for a single optical source to fan its signals out to a very large number of recipients. This fan-out can be implemented in free space, over fiber optic networks, or in dielectric waveguides at the chip and wafer scales. For large neural systems, it will be advantageous to employ all these media for signal routing. The presence of excellent waveguiding materials and a variety of light sources inclines us to utilize optical signals with  $1 \mu m \le \lambda \le 2 \mu m$ . Additionally, because the energy of a photon and its wavelength are inversely proportional, optoelectronic circuits face a power/ area trade-off. Similar circuits to those presented here could be implemented with microwave circuits, but the system size would likely be cumbersome. Operation near telecommunication wavelengths appears to strike a suitable compromise.

## 2. Superconducting electronics

The foundational conjecture of the proposed hardware platform is that light is optimal for communication in cognitive systems. The subsequent conjecture is that power consumption will be minimized if single photons of light can be sent and received as signals between neurons in the system. Superconducting single-photon detectors are

the best candidate for receiving the photonic signals. In addition to selecting microscale light sources and dielectric waveguides, we choose to utilize superconduting-nanowire single-photon detectors<sup>58-61</sup> to receive photonic signals because of the speed,<sup>62</sup> efficiency,<sup>61</sup> and scalable fabrication<sup>63</sup> of these devices.

Utilizing superconducting single-photon detectors contributes to energy efficiency in three ways. First, because a single photon is a quantum of the electromagnetic field, it is not possible to signal with less energy at a given wavelength. Second, because the device is superconducting, it dissipates near zero power when it is not responding to a detection event. Third, the power dissipated by the detector during a detection event is on the order of the energy used to generate the photon being detected, so a significant additional energy penalty is not incurred.

The choice of employing superconductors has several important ramifications. It requires that we operate at temperatures that support a superconducting ground state ( $\approx 4\,\mathrm{K}$ ), so cryogenic cooling must be implemented. While cooling is an inconvenience, employment of superconducting detectors brings the opportunity to utilize the entire suite of superconducting electronic devices,  $^{64-66}$  including JJs and thin-film components such as current  $^{67,68}$  and voltage  $^{69}$  amplifiers. Semiconductor light sources also benefit from low temperature,  $^{70}$  and silicon light sources become an option.  $^{63}$

We have emphasized that the charge and mass of electrons are a hindrance for communication. Yet, the interactions between electrons due to their charge make them well suited to perform the computation and memory functions of synapses and neurons. In particular, superconducting devices and circuits are exceptionally capable of achieving the complex dynamical systems necessary for cognition. To elucidate the specific type of dynamical devices we intend to employ, we now elaborate upon the strengths of relaxation oscillators for cognitive systems.

## 3. Relaxation oscillators

A defining aspect of cognitive systems is the ability to differentiate locally to create many subprocessors, but also to integrate the information from many small regions into a cohesive system, and to repeat this architecture across many spatial and temporal scales. A network of many dynamical nodes, each with the capability of operating at many frequencies, gives rise to a vast state space. As computational primitives that can enable such a dynamical system, oscillators are ideal candidates. In particular, relaxation oscillators 18,3 with temporal dynamics on multiple time scales<sup>37</sup> have many attractive properties for neural computing, which is likely why the brain is constructed of such devices.<sup>74</sup> We define a relaxation oscillator as an element, circuit, or system that produces rapid surges of a physical quantity or signal as the result of a cycle of accumulation and discharge. Relaxation oscillators are energy efficient in that they generally experience a long quiescent period followed by a short burst of activity. Timing between these short pulses can be precisely defined and detected. Relaxation oscillators can operate at many frequencies<sup>38</sup> and engage with myriad dynamical interactions. 49 The oscillator's response is tunable, 38 they are resilient to noise because their signals are effectively binary,<sup>75</sup> and they can encode information in their mean oscillation frequency as well as in higher-order timing correlations.1

The relaxation oscillators we intend to employ as the computational primitives of superconducting optoelectronic networks can be as simple as integrate-and-fire neurons<sup>39,41</sup> or more complex with the addition of features such as dendritic processing<sup>14,77–80</sup> to inhibit specific sets of connections<sup>17,18,52</sup> or detect timing correlations and sequences of activity. <sup>14,80</sup> While our choice to use superconductors was motivated by the need to detect single photons, we find superconducting circuits combining SPDs and JJs are well suited for the construction of relaxation oscillators with the properties required for neural circuits.

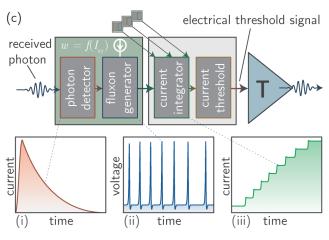

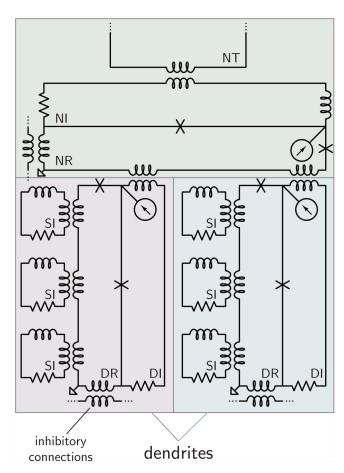

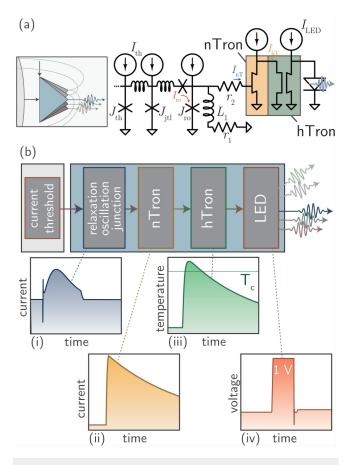

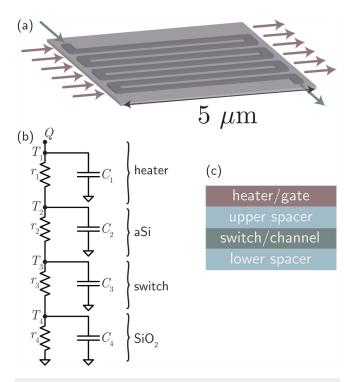

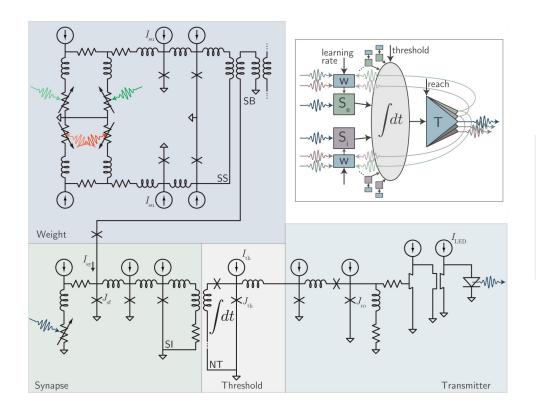

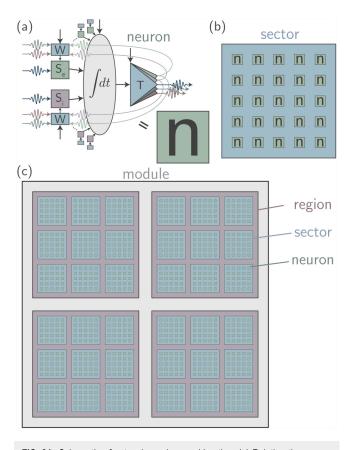

## 4. Neuron overview

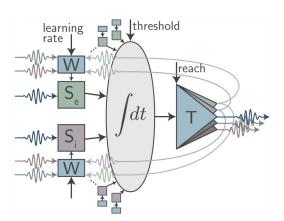

We refer to relaxation oscillators sending few-photon signals that are received with superconducting detectors as superconducting optoelectronic neurons. In the specific neurons studied in this work, integration, synaptic plasticity, and dendritic processing are implemented with inductively coupled loops of supercurrent. We refer to devices of this type as loop neurons. The loop neuron presented in this paper is shown schematically in Fig. 1. A full circuit diagram is shown in Fig. 23. The remainder of this section is an overview of the circuits described in more detail in the rest of the paper. Operation of loop neurons is summarized as follows.

Photons from upstream neurons are received by superconducting SPDs at a neuron's synapses. Using Josephson circuits, these detection events are converted into an integrated supercurrent which is stored in a superconducting loop. The amount of current that gets added to the integration loop during a photon detection event is determined by the synaptic weight. The synaptic weight is dynamically adjusted by another circuit combining SPDs and JJs. When the integrated current of a given neuron reaches a (dynamically variable) threshold, an amplification cascade begins, resulting

**FIG. 1.** Schematic diagram of a loop neuron showing excitatory  $(S_e)$  and inhibitory  $(S_i)$  synapses, as well as synaptic weight update circuits (W). The wavy, colored arrows are photons, and the straight, black arrows are electrical signals. The synapses receive signals as faint as a single photon and add supercurrent to an integration loop. Upon reaching threshold, a signal is sent to the transmiter circuit (T), which produces a photon pulse. Some photons from the pulse are sent to downstream synaptic connections, while some are used locally to update synaptic weights.

in the production of light from a waveguide-integrated semiconductor light emitter. The photons thus produced fan out through a network of dielectric waveguides and arrive at the synaptic terminals of other neurons where the process repeats.

In these loop neurons, a synapse consists of an SPD in parallel with a JJ (which together transduce photons to supercurrent), and a superconducting loop, which stores a current proportional to the number of detected photon arrival events. This loop is referred to as the synaptic integration (SI) loop. Within each neuron, the loops of many synapses are inductively coupled to a larger superconducting loop, referred to as the neuronal receiving (NR) loop, thereby inducing an integrated current proportional to the current in all the neuron's synapses. When the current in this NR loop reaches a threshold, the neuron produces a current pulse in the form of a flux quantum. This current is amplified and converted to voltage to produce photons from a semiconductor p-i-n junction.

The currents in the synaptic and neuronal loops are analogous to the membrane potential of biological neurons,<sup>41</sup> and the states of flux in these loops are the principal dynamical variables of the synapses and neurons in the system. Inhibitory synapses can be achieved through mutual inductors with the opposite sign of coupling. Dendritic processing can be implemented straightforwardly by adding intermediate mutually inductively coupled loops between the synaptic and neuronal loops. Synapses can be grouped on dendritic loops capable of local, nonlinear processing and inhibition.1 Dendrites capable of detecting specific sequences of synaptic firing events<sup>77,80</sup> can also be achieved. Neurons with multiple levels of dendritic hierarchy can be implemented as multiple stages of integrating loops. Clustering synapses on multiple levels of hierarchy in this way enables information access at gradually larger length scales across the network through transient synchronization at gradually lower frequencies. 28 The temporal scales of the loops can be set with L/rtime constants, so different components can operate on different temporal scales, enabling relaxation oscillators with rich temporal dynamics. These relaxation oscillators can be combined in networks with dynamic functional connectivity, reconfigurable through inhibition and synaptic plasticity.<sup>50</sup> <sup>2</sup> These receiver circuits and integration loops are presented in Sec. II.

Synaptic memory is also implemented based on the stored flux in a loop, referred to as the synaptic storage (SS) loop. The state of flux in the SS loop determines the current bias to the synaptic receiver circuit discussed above. This current bias is the synaptic weight. If the SS loop is created with a superconducting wire of high inductance, the loop can hold many discrete states of flux and, therefore, can implement many synaptic weights. In Sec. III, we investigate synapses with a pseudocontinuum of hundreds of stable synaptic levels between minimal and maximal saturation values, and we show that transitions between these levels can be induced based on the relative arrival times of photons from the presynaptic and postsynaptic neurons, thereby establishing a means for spike-timing-dependent plasticity (STDP) with one photon required for each step of the memory-update process.

While synapses with many stable levels are advantageous to extending memory retention times, <sup>55</sup> it is also important to implement synapses that change not only their efficacy based on preand postsynaptic spike timing but also their probability of changing their efficacy. <sup>54</sup> Just as the synaptic weight is adjusted through a

current bias on the receiver circuit, the probability of changing the synaptic weight can be adjusted through a current bias on the synaptic update circuit. As in the dendrites, we see a hierarchy can be achieved. In the case of synaptic memory, the synaptic weight and its rates of change are implemented in a loop hierarchy, and the state of flux in the loops can be dynamically modified based on photons generated by neural activity. Similar mechanisms can be utilized to adjust the synaptic weight based on short-term activity from the presynaptic neuron 81 or on a slowly varying temporal average of the postsynaptic activity. 82,83 The synaptic memory circuits we develop in Sec. III are logical extensions of binary memory cells utilized in superconducting digital electronics. 65,666

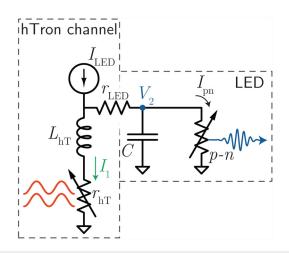

The aspect of superconducting optoelectronic neuron operation that is most difficult to achieve is the production of light. The superconducting electronic circuits that perform the aforementioned synaptic and neuronal operations operate at millivolt levels, whereas the production of the near-infrared photons desirable for communication requires a volt across a semiconductor diode. When a neuron reaches threshold, an amplification sequence begins. Current amplification is first performed, and the resulting large supercurrent is used to induce a superconducting-to-normal phase transition in a length of wire. When the current-biased wire becomes resistive, a voltage is produced via Ohm's law. This device leverages the extreme nonlinearity of the quantum phase transition to quickly produce a large voltage and an optical pulse. These transmitter circuits are discussed in Sec. IV.

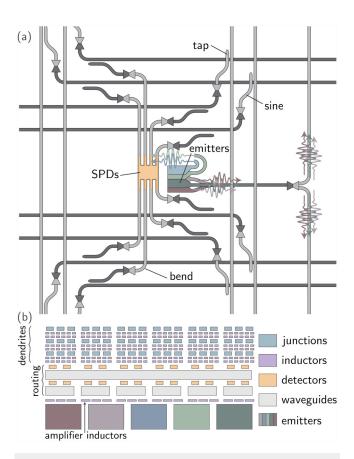

The photons of a neuronal pulse are distributed over a large axonal network of passive dielectric waveguides. These waveguides terminate at each of the downstream synaptic connections. A downstream synaptic firing event will occur with near-unity probability at any connection receiving one or more photons. Photons of multiple colors can be generated simultaneously or independently, and different colors can share routing waveguides, while being used for different functions on the receiving end, such as synaptic firing and synaptic update. The number of photons produced during a neuronal firing event determines the probability that distant connections will receive the signal, and this reach can be manipulated with the current bias to the light emitter. The network of waveguides that routes the communication events is discussed in Sec. V.

To make the analogy to biological neural hardware explicit, synapses are manifest as circuits comprising superconducting SPDs with JJs. These synapses transduce photonic communication signals to supercurrent for information processing, and this supercurrent plays the role of the membrane potential. The dendritic arbor is a spatial distribution of synapses interconnected with inductively coupled loops for intermediate integration and nonlinear processing. The integration function of the soma is also achieved with a superconducting loop, and the threshold is detected when a JJ in this loop is driven above its critical current. The firing function of the soma (or axon hillock) is carried out by a chain of superconducting current and voltage amplifiers that drive a semiconductor diode to produce light. The axonal arbor is manifest as dielectric waveguides that route photonic signals to downstream synaptic connections. Gap junctions may be realized with evanescent couplers between waveguides of the axonal arbor, but we do not consider gap junctions further in this paper.

Loop neurons combine several core devices: superconducting single-photon detectors, <sup>58–61</sup> Josephson junctions, <sup>64–66</sup> superconducting

mutual inductors, 84 superconducting current 67,68 and voltage amplifiers,<sup>69</sup> semiconductor light sources,<sup>1,63</sup> and passive dielectric waveguide routing networks. 85-87 While all the components of these neurons have been demonstrated independently, their combined operation has not been shown. The experimental effort to achieve circuit integration is underway. The physical principles of their operation and the designs presented in this paper indicate the potential for loop neurons to achieve complex, large-scale systems. The straightforward implementation of inhibition; the realization of a variety of temporal scales through L/r time constants; single-photon-induced synaptic plasticity; and dynamically variable learning rate, threshold, and reach indicate these relaxation oscillators are promising as computational primitives. In conjunction with dense local and fast distant communication over passive waveguides, the system appears capable of the spatial and temporal information integration necessary for cognition and binding.

We do not propose superconducting optoelectronic networks (SOENs) as an alternative to established neural hardware, but rather as a symbiotic technology. The success of neural CMOS (including optical communication above a certain spatial scale) will contribute to the success of SOENs, as it will be advantageous for SOENs to interface with CMOS via photonic signaling over fiber optic links between cryogenic and ambient environments. SOEN hardware is particularly well suited to interfacing with other cryogenic technologies such as imaging systems with superconducting sensors, 88,8 are commonly employed for medical diagnostics, 90 exoplanet search, 91-93 cosmology, 94 and particle detectors. 95 Another intriguing application is in conjunction with other advanced computing technologies such as flux-based logic<sup>96–98</sup> and quantum computers. One can envision a hybrid computational platform <sup>104,105</sup> wherein a quantum module utilizes entanglement and superposition, while a neural module performs quantum-limited measurements and learns the behavior of the quantum system, and classical fluxon logic controls the operation of both. A superconducting optoelectronic hardware platform is likely to satisfy the computation and communication requirements of this hybrid technology.

At this point, we have described the motivations for loop neurons, and we have summarized their operation. The remainder of the document contains technical details of circuit operations (Secs. II–IV) and scaling analysis (Sec. V).

## **II. SYNAPTIC RECEIVER CIRCUITS**

The focus of this section is on the conversion of photonic communication events on many synapses to an integrated total signal stored in the neuron. These optoelectronic devices must meet several criteria: (1) the neuron must be able to achieve leaky integrate-and-fire functionality<sup>39,41</sup> wherein activity on multiple synapses contributes to an integrated signal with a controllable leak rate; (2) single-photon detection events must contribute to the integrated signal, and the amount each detection event contributes to the integrated signal should depend on a dynamically reconfigurable synaptic weight; (3) neurons that are sensitive to the sum of spike events must be achievable in order to make use of rate-coded signals, <sup>106</sup> and neurons that are sensitive to the timing between afferent spikes must also be achievable in order to make use of

temporal coding; 14,39,75,77 (4) the circuits must scale to thousands of synaptic connections to integrate information across moderately sized cognitive circuits; 180 (5) the dynamic range of the neuron and synapses should allow activity on a large fraction of the synapses to contribute to a neuronal firing event, yet repeated activity on a small fraction of the synapses should also be able to induce a neuronal firing event; (6) synapses with inhibitory as well as excitatory functionality must be achievable, and inhibition must work in conjunction with dendrites 17,18,80 to enable synchronization on multiple time scales. 14-17,52 This section explores circuit designs satisfying these criteria.

## A. Circuit operation

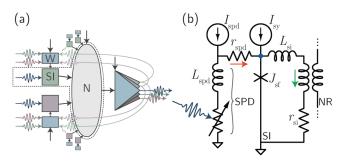

The synaptic receiver is enclosed within the dashed boundary of Fig. 2(a). A simple instantiation of the synaptic circuit is shown in Fig. 2(b), and the operation of the synapse is illustrated schematically in Fig. 2(c). This receiver circuit in the context of the other

FIG. 2. (a) Schematic of the neuron, as shown in Fig. 1. Here, the dashed line encloses the synaptic receiver and neuronal loop that we describe in this section. (b) Circuit diagram of a simple photon-to-fluxon transducer combining a single-photon detector, Josephson junction, and flux-storage loop. (c) Sequence of events during the synaptic firing event. (i) Single-photon detector transduces photon to electrical current. (ii) Fluxons produced when SPD diverts current to JJ. The number of fluxons is determined by the synaptic bias current, which is controlled by the box labeled W in (a), discussed in Sec. III. (iii) Fluxons added to the integration supercurrent storage loop. When the current in the loop reaches threshold, an electrical signal is sent to the transmitter.

components of the neural circuit is shown in Fig. 23 in Sec. IV. The synaptic receiver circuit comprises an SPD in parallel with a JJ embedded in a flux-storage loop. This design is a reasonable starting point for a single-photon-sensitive synapse because it achieves transduction of a photonic signal to a superconducting electronic signal with a simple circuit. The design is similar to other superconducting particle detector circuits, such as transition-edge bolometers.<sup>6</sup>

The operation of the synaptic circuit proceeds as follows. The SPD, shown as a variable resistor in series with an inductor in Fig. 2(b), has zero resistance in the steady state, and it switches to a high-resistance state temporarily upon absorption of a photon. When a photon is detected, an electrical current is diverted from the SPD to a JJ, referred to as the synaptic firing junction ( $J_{sf}$ ). The current diverted from the SPD [Fig. 2(c), part (i)] causes the net current through  $J_{\rm sf}$  to exceed  $I_{\rm c}$ , generating a series of fluxons [Fig. 2(c), part (ii)]. We refer to this detection of a photon by the SPD and subsequent generation of fluxons by the JJ as a synaptic firing event. The synaptic weight of the connection is implemented via the current bias across  $J_{\rm sf}$ , controlled by  $I_{\rm sv}$ . The effect of this synaptic weight is to change the duration the JJ bias current exceeds I<sub>c</sub>, and, therefore, the number of fluxons generated during a synaptic firing event. If the synaptic weight is weak, a small number of fluxons, and, therefore, a small total amount of supercurrent, will be generated. If the synaptic weight is strong, a large number of fluxons, and, therefore, a large amount of supercurrent, will be generated during the synaptic firing event. The SPD response is virtually identical whether the number of photons present is one or greater than one, and for energy efficiency, it is advantageous to send the fewest number of photons possible to each synaptic connection. The SPD response also does not depend strongly on the frequency of light across a bandwidth broad enough for multiplexing.61 Implementing synaptic weight in the electronic domain in this manner makes use of both the speed and energy efficiency of JJs, while leveraging the strengths of light for communication.

The supercurrent generated during each synaptic firing event is added to a superconducting loop, called the synaptic integration (SI) loop, which integrates the total current from all synaptic firing events at that synapse [Fig. 2(c), part (iii)]. Many synapses will be coupled to a larger neuronal receiving (NR) loop via mutual inductors. The NR loop combines the signals from all the synapses connected to the neuron. Ultimately, the current coupled to the NR loop is increased using a current transformer that induces current in a final loop, the neuronal thresholding (NT) loop. The NT loop is a superconducting loop that contains a JJ  $(J_{\rm th})$  that produces an output current pulse when its critical current (threshold) is reached. This threshold can be dynamically varied with a current bias. The current pulse generated when the neuron reaches threshold is amplified and ultimately used to trigger a photon-generation event.

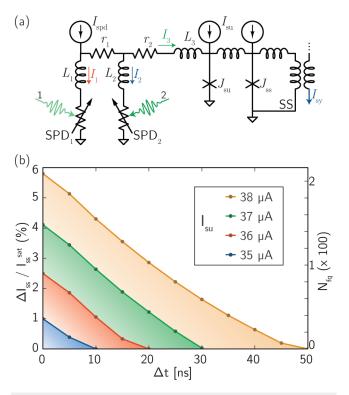

The number of flux quanta generated in a synaptic firing event depends on the relation between  $I_c$ ,  $I_{spd}$ , and  $I_{sy}$ , as well as the SPD time constant,  $L_{\rm spd}/r_{\rm spd}$ . If the bias current I is close to but greater than  $I_c$ , the time-averaged voltage across the junction will be given by  $\langle V \rangle \approx R \sqrt{I^2 - I_c^2}$ , (in the limit of an overdamped junction<sup>66</sup>) where *R* is the junction resistance in the nonsuperconducting state. The rate of generation of flux quanta is given by  $r_{\rm fq} = \langle V \rangle /\Phi_0$ . This generated flux is trapped in the SI loop. The utilization of a JJ in this

circuit is advantageous to decouple the amount of current added to the loop from the time it is stored in the loop. The current in each SI loop decays with the  $\tau_{\rm si}=L_{\rm si}/r_{\rm si}$  time constant, which can be chosen over a broad range. By choosing  $\tau_{\rm si}$  to be different for different synapses, one can diversify the temporal information provided to the neuron.  $^{17,28,30,81}$

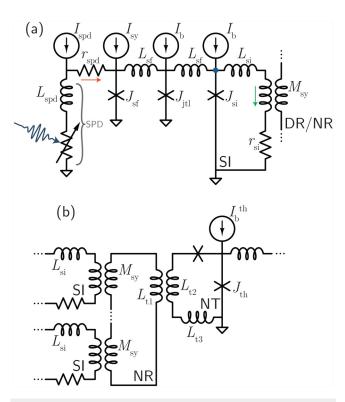

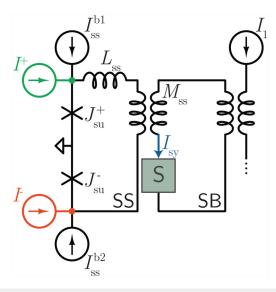

The circuit of Fig. 2(b) captures the concept of the receiver, but its performance is limited in this configuration because the SI loop saturates at a small current. Higher saturation current is achieved by separating the transduction operation from the SI loop by a Josephson transmission line (JTL), <sup>65,66</sup> as shown in Fig. 3(a). This form of the receiver circuit is the form used as a synapse in this work.

In the configuration of Fig. 3(a), the fluxons produced by the switching of  $J_{\rm sf}$  during a synaptic firing event propagate down a JTL (a single JJ in this study) and drive the switching of a junction inside the SI loop. The fluxons from multiple synaptic firing events can be stored in the SI loop, and, therefore, we may wish to use a loop that can contain many fluxons. The current added to the loop by a single

**FIG. 3.** (a) Circuit diagram of the photon-to-fluxon transducer connected to the synaptic integration (SI) loop by a JTL. The photon-to-fluxon transducer combines a single-photon detector (SPD) with the synaptic firing junction ( $J_{sf}$ ). The synaptic weight is established with the synaptic bias current ( $I_{sy}$ ). Fluxons traverse the Josephson transmission line ( $J_{jt}$ ) and enter the synaptic integration loop. The SI loop couples to a dendritic receiving (DR) loop or directly to the neuronal receiving (NR) loop. (b) Circuit diagram of multiple synapses (SI loops) connected to the NR loop and the neuronal thresholding (NT) loop through mutual inductors ( $M_{sy}$ ). The thresholding junction ( $J_{th}$ ) detects neuronal threshold, which is dynamically configurable with the threshold bias current ( $I_{th}^{th}$ ).

fluxon is  $I_{\phi} = \Phi_0/L_{\rm si}$ , where  $\Phi_0 = h/2e = 2.07 \times 10^{-15}$  Wb is the magnetic flux quantum. The SI loop can maintain a linear response in the presence of many synaptic firing events if  $L_{\rm si}$  is chosen to be large, or the SI loop can saturate if  $L_{\rm si}$  is chosen to be small, thus providing one means of implementing short-term plasticity.<sup>81</sup>

The SI loops are inductively coupled to the NR loop, [Fig. 3(b)], which stores a current proportional to a weighted sum of the currents in all the SI loops. The use of mutual inductors allows many synapses to add current to an NR loop without introducing leakage current pathways. Finally, the NR loop couples to a third loop, the NT loop. The mutual inductor coupling the NR loop to the NT loop serves as a transformer to step up the current to be detected at threshold. The NT loop may not need to be a separate loop when the number of synapses,  $N_{\rm sy}$ , is small. The performance of the NT loop upon reaching current threshold is discussed in Sec. IV.

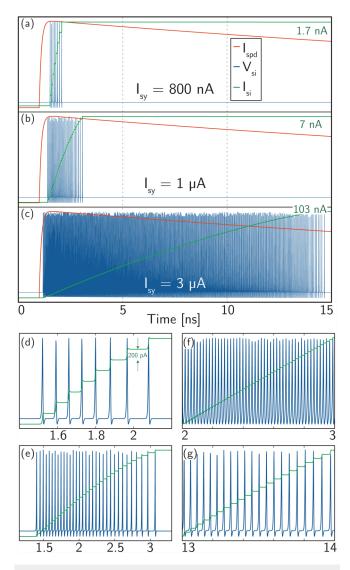

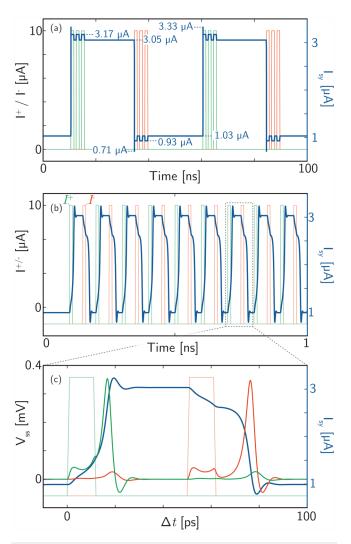

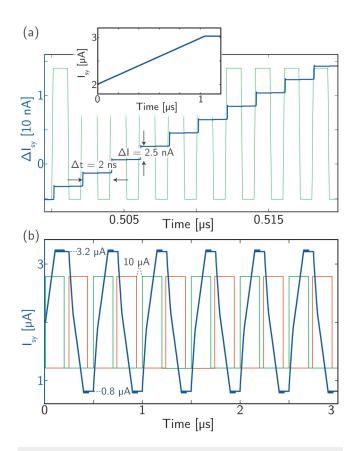

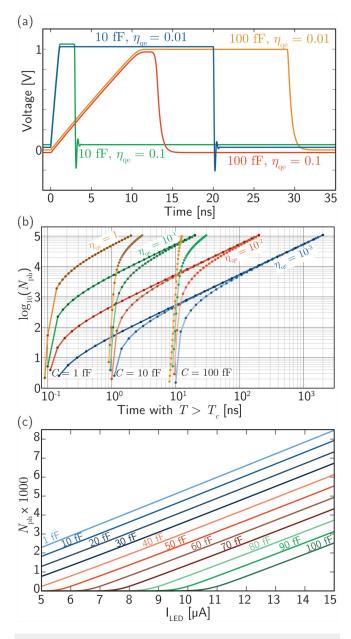

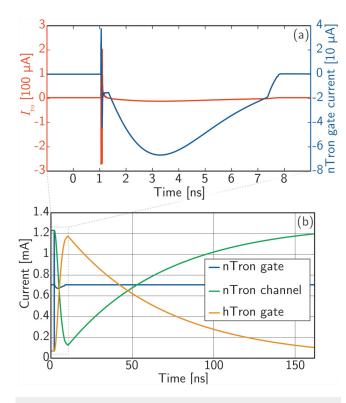

In Fig. 4, we simulate the operation of the synaptic receiver as it experiences a synaptic firing event. We use WRSpice<sup>109</sup> to model the circuit of Fig. 3(a). We treat the SPD as a current source with exponential rise with 100 ps time constant followed by exponential decay with 50 ns time constant. The amplitude of the SPD current pulse is 10 µA. All circuit parameters used in this work are given in Appendix A. Figures 4(a)-4(c) show the activity of a synaptic firing event for  $I_{sy} = 800 \,\text{nA}$ ,  $1 \,\mu\text{A}$ , and  $3 \,\mu\text{A}$ . With  $I_{sy} = 800 \,\text{nA}$ , the junction is briefly driven above  $I_c$ , and eight fluxons are transmitted to the SI loop. The synaptic firing event causes the current in the SI loop,  $I_{si}$ , to increase by 1.7 nA. If we increase the bias current to  $I_{\rm sy}=1\,\mu{\rm A}$ , the synaptic firing event produces 33 fluxons and adds 7 nA to the SI loop. Further increasing the synaptic bias (SB) to  $3 \mu A$  gives the behavior shown in Fig. 4(c). In this case, 497 fluxons add 103 nA to the SI loop. The period of the voltage pulses is observed to decrease through the duration of the SPD pulse, demonstrating the decrease of  $r_{\rm fq}$  as current returns to the SPD and the net bias across the JJ decays, as discussed above. Details of synaptic firing are shown in Figs. 4(d)-4(g). The energy consumed by a synaptic firing event is discussed in Appendix A.

The analysis of Fig. 4 gives the currents and voltages present during a synaptic firing event for three values of  $I_{sy}$ . Systematic analysis of  $I_{si}$  vs  $I_{sy}$  finds a quadratic trend. A principal objective of this analysis is to determine the range of synaptic bias currents over which we would like to operate. Operating with a minimum synaptic bias of  $1 \mu A$  enables us to work close to the energy-efficiency limit of the circuit, and we anticipate that the exact number of fluxons produced during a firing event will be noisy, much like the activity of a biological neuron. The amount of current added to the SI loop during a synaptic firing event with strong synaptic weight should be significantly larger than the amount of current with a weak synaptic weight. We choose  $I_{sy} = 3 \mu A$  to be the largest synaptic bias at which we would like to operate, and thus, a synaptic firing event with a strong synaptic bias adds 15 times as much current to the SI loop (and, therefore, the NR loop and the NT loop) as a firing event with a weak synaptic bias. This ratio is entirely tunable based on the needs of the system. Learning-either supervised or unsupervised-should adjust the synaptic bias current over the range  $1 \mu A < I_{sy} < 3 \mu A$ for the parameters considered here. Circuits accomplishing this are discussed in Sec. III.

In the circuit of Fig. 3(a), synaptic activity can result in saturation of the SI loop, wherein additional synaptic firing activity adds

**FIG. 4.** Operation of the synaptic firing circuit during a synaptic firing event for three values of  $I_{\rm sy}$ . The three traces in each of these plots are normalized such that the maximum of each trace within the displayed time window is set to one and the minimum is set to zero. The colors of the traces are in reference to the current paths and voltage node labeled in Fig. 3(a). (a) Activity of the synaptic firing circuit for  $I_{\rm sy}=800\,{\rm nA}$ . (b) Activity of the synaptic firing circuit for  $I_{\rm sy}=1\,\mu{\rm A}$ . (c) Activity of the synaptic firing circuit for  $I_{\rm sy}=3\,\mu{\rm A}$ . (d) Temporal zoom for  $I_{\rm sy}=800\,{\rm nA}$ . (e) Temporal zoom for  $I_{\rm sy}=3\,\mu{\rm A}$ . (g) Temporal zoom near the beginning of the photon-detection pulse for  $I_{\rm sy}=3\,\mu{\rm A}$ . (g) Temporal zoom near the end of the photon-detection pulse for  $I_{\rm sy}=3\,\mu{\rm A}$ .

no additional current to the loop. The value of  $I_{\rm si}$  at which saturation occurs can be controlled in circuit design, and in the present work, it is near  $10\mu\rm A$ . The amount of current added to the loop by a single fluxon is given by  $\Delta I_{\rm si} = \Phi_0/L_{\rm si}$ , so the number of synaptic firing events that cause saturation can be adjusted across a broad range. With a small value of  $L_{\rm si}$ , a single synapse event can saturate

the loop, and with a large value, the loop can maintain a linear response in the presence of many repeated synapse events. The SI loop with the design described above can receive over 1000 synaptic firing events when  $I_{\rm sy}=1\,\mu{\rm A}$ , and 82 synaptic firing events when  $I_{\rm sy}=3\,\mu{\rm A}$  before saturation of the loop occurs (assuming  $L_{\rm si}=10\,\mu{\rm H}$  and  $\tau_{\rm si}\to\infty$ ). If the loop contains a resistance, the trapped flux will leak with the L/r time constant, leaving the synapse ready to receive further synaptic firing events.

#### B. Multisynaptic neurons

In general, a neuron will combine signals from many synaptic connections and produce a pulse when this combined signal reaches a threshold. We would like to know how devices will perform when many synapses are integrated with a single NR loop. An important question is how many SI loops must receive activity to drive the NT loop to threshold. We have analyzed the current induced in the NT loop as a function of the number of synapses inductively coupled to the NR loop. We find that with symmetrical mutual inductors of 100 pH, if the NR loop receives 1000 inputs, a saturated SI loop will still induce nearly 500 nA in the NT loop. If the NT loop requires  $5\mu$ A to threshold (a number comfortably above the noise level), then 10 saturated synapses can cause the neuron to fire. Evidence from neuroscience indicates that a neuron with N synapses is commonly driven to fire by activity on  $\sqrt{N}$  synapses (with significant diversity in responses observed), and this analysis finds that coupling through mutual inductors makes the required synaptic strength possible, even when 1000 connections are made to a single NR loop. Further improvement is likely possible with asymmetric mutual inductors. Perhaps more importantly, in mature network architectures, neurons receiving input from thousands of synapses are likely to employ a complex dendritic tree. It is unlikely that any one dendrite will receive activity from 1000 synapses, and the range of synaptic efficacy achievable with these circuits is wellmatched to the threshold current levels that will be convenient in practice.

We wish to know how inductively coupling multiple SI loops to a single NR loop affects the operation during synaptic firing events with regard to cross talk. Cross talk between synapses is small in this configuration, primarily because the self-inductance of each SI loop  $(L_{si})$  is much larger that the mutual inductance between each SI loop and the NR loop  $(M_{\rm sy})$ . For example, a typical value for  $L_{si}$  is on the order of 100 nH, while a typical value for  $M_{\rm sy}$  is on the order of 100 pH. To arrive at analytical expressions for the cross talk between two SI loops coupled to the same NR loop, we assume that one synapse experiences a synaptic firing event, current is added to that SI loop, and we ask how much current is induced in the other SI loops due to their mutual coupling to the same NR loop. In the limit that  $L_{\rm si} \gg M_{\rm sy}$ , this induced parasitic current scales as  $M_{\rm sv}/(N_{\rm sv}L_{\rm si})$ , where  $N_{\rm sv}$  is the total number of synapses (SI loops) coupled to the same NR loop. For typical values of  $M_{\rm sy}$  and  $L_{\rm si}$ , this quantity is on the order of  $10^{-3}$  for  $N_{\rm sy}=1$  and decreases as synapses are added to the loop. Therefore, cross talk between SI loops coupled to the same NR loop is not problematic with this fan-in design. We may also ask about the ratio of the intended current induced in the NR loop to

the parasitic current induced in adjacent SI loops. This quantity is independent of  $N_{\rm sy}$ , and in the same limit of  $L_{\rm si} \gg M_{\rm sy}$ , we find that the ratio of the current induced in adjacent SI loops to the current induced in the NR loop is  $M_{\rm sy}/L_{\rm si}$ , which again is on the order of  $10^{-3}$  for typical circuit parameters.

We have further investigated this cross talk numerically. WRSpice simulations show that a synaptic firing event of a neuron with a single synaptic connection and a synaptic firing event of a single synapse connected to an NR loop with 10 synaptic connections produce an identical number of fluxons with identical timing. The effect of timing delay between two synaptic firing events on different synapses in a neuron of  $N_{\rm sy}=10$  has also been considered. The total current added to the NR loop is independent of the timing delay between the two synaptic firing events. These linearities with respect to  $N_{\rm sy}$  and pulse timing delay are attractive features of inductively coupled synapses. Contexts in which nonlinearity with respect to arrival time is desirable, such as for temporal coding 14,77 or dendritic processing, 79,80 are likely to employ two-photon receiver circuits or dendritic loops as discussed in Sec. II C.

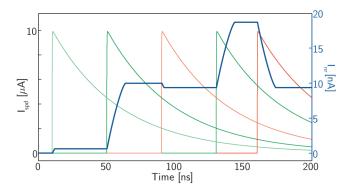

It is important for a neuron to be able to receive excitatory and inhibitory connections.  $^{41,52,110,112}$  Inhibitory connections keep the network from experiencing runaway activity and are crucial for temporal synchronization.  $^{14-18}$  Inhibitory connections can be constructed with the same photon-to-fluxon transduction circuit presented thus far by changing the sign of  $M_{\rm sy}$ . We investigate a neuron with seven excitatory and three inhibitory connections in Fig. 5. The figure shows a time trace of  $I_{\rm ni}$  as three excitatory and two inhibitory synaptic firing events occur. An excitatory event and an inhibitory event occur in synapses with  $I_{\rm sy}=1\,\mu{\rm A}$ , and the other events occur in synapses with  $I_{\rm sy}=3\,\mu{\rm A}$ . This plot

**FIG. 5.** A neuron with seven excitatory and three inhibitory synaptic connections. The excitatory and inhibitory current inputs are shown as green and red traces and are referenced to the left y axis. The blue trace is  $l_{\rm sy}$ , referenced to the right y axis. At time t=10 ns, a synaptic firing event occurs on an excitatory synapse with  $l_{\rm sy}=1\,\mu{\rm A}$ . At time t=50 ns, a synaptic firing event occurs on an excitatory synapse with  $l_{\rm sy}=3\,\mu{\rm A}$ . At time t=90 ns, a synaptic firing event occurs on an inhibitory synapse with  $l_{\rm sy}=1\,\mu{\rm A}$ . At time t=130 ns, a synaptic firing event occurs on an excitatory synapse with  $l_{\rm sy}=3\,\mu{\rm A}$ . At time t=160 ns, a synaptic firing event occurs on an inhibitory synapse with  $l_{\rm sy}=3\,\mu{\rm A}$ . The colors in this plot are not in reference to Fig. 3.

demonstrates the dynamic state of a multisynaptic neuron under the influence of excitation and inhibition.

The symmetry between inhibitory and excitatory synapses is broken by  $I_{\rm b}^{\rm th}$ , the current bias across the thresholding junction. The circuit can be designed so the saturation of all inhibitory SI loops is insufficient to add enough counter current to the NT loop to overcome  $I_{\rm b}^{\rm th}$  and reach threshold. Thus, repeated excitatory events can drive the neuron to spike, but repeated inhibitory events can only move the device further from threshold and cannot trigger a spike, much like the polarizing effects of inhibitory interneurons in biological neural systems.

## C. Dendritic processing

In addition to neurons that integrate single-photon pulses, as described in Sec. II A, it is desirable to achieve neurons that detect coincident signals from two or more presynaptic neurons for detecting temporally coded information. 14,77-80,113 The mutual information regarding a stimulus conveyed by two or more neurons can be approximated by a Volterra expansion<sup>39</sup> with the leading term corresponding to firing rate, and the second-order term representing correlations. <sup>76</sup> In biological neurons, temporal synaptic sequences can be detected using hardware nonlinearities present in dendrites, <sup>79,80</sup> which perform important cortical computations. Detection of timing correlations and sequences can be achieved in optoelectronic hardware using two (or more) SPDs in a similar circuit to the synaptic receiver of Fig. 3(a).

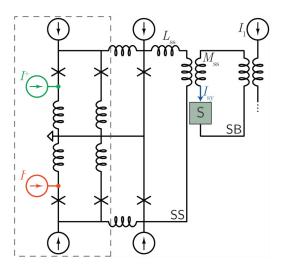

In Fig. 6, we analyze a two-photon symmetrical coincidence detection circuit. The circuit diagram is shown in Fig. 6(a). The two SPDs are biased symmetrically, and the circuit is designed such that if either SPD detects a photon in isolation, the current across  $I_{\rm sf}$  remains below  $I_{\rm c}$ , but if both detect a photon within a certain time window, the current across  $J_{sf}$  can exceed  $I_c$ , adding current to the SI loop. The amount of current added to the SI loop is plotted as a function of the difference in arrival times between two photons in Fig. 6(b). WRSpice was again used for these simulations, but in this case, the SPDs were modeled not as current sources but as resistors of  $5\,k\Omega$  with 200 ps duration occurring at specified photon-arrival times.<sup>62</sup> The time scale over which correlated events are detected is set by the  $L_{\rm spd}/r_{\rm spd}$  time constant of the circuit. In the main panel, this time constant is 500 ns, and in the inset, it is 50 ns. Longer correlation windows can be straightforwardly achieved, and the shortest correlation window will be limited by the latching time of the SPDs.

Due to the symmetric biasing of the two SPDs, the circuit of Fig. 6 is insensitive to order of photon arrival. By breaking this symmetry, similar receiver circuits that detect ordered correlations can be used for Hebbian learning. The two-SPD circuit of Fig. 6 can also be extended to detect other sequences of activity, including sequences with more photons.

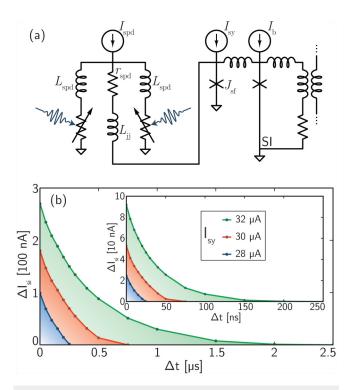

Dendritic processing can also be used for intermediate nonlinear processing between synapses and the NR loop. <sup>114</sup> An example circuit is shown in Fig. 7. Here, multiple SI loops are inductively coupled to another loop, which contains a JJ. Only when the junction is driven above its critical current does an appreciable signal get added to the dendritic integration (DI) loop, which is an intermediate, nonlinear processor between the SI loop and the NR loop.

FIG. 6. Coincidence detection circuit for neurons sensitive to temporal coding. (a) Circuit diagram of symmetric two-photon coincidence detection circuit. (b) Current added to the SI loop as a function of time delay between arrival of the photons. Performance was calculated for the three values of  $I_{\rm SV}$  shown in the legend. Circuit parameters are given in Appendix A.

In this case, the DI loops are analogous to dendrites. An important role of dendrites is in conjunction with inhibitory interneurons that can temporarily suppress the efficacy of an entire dendrite. 17,18,52 At the bottom of Fig. 7, we show how an inhibitory interneuron may be inductively coupled to a dendrite. When inhibition is applied to the loop, it may be impossible for the synaptic connections to drive the JJ above threshold and add flux to the DI loop. Many levels of loop hierarchies can be combined in this way to achieve various nonlinear functions as well as current amplification before the NT loop.

Dendritic processing in conjunction with inhibitory interneurons contributes to network synchronization on various temporal and spatial scales. 14-16,18,27,52 The approach to dendrites shown in Fig. 7 is one way inhibition could be used with the synapses presented here to achieve these functions thought to be necessary for cognition. 17,50 In this context, engineering synaptic and dentritic circuits with a variety of time constants (analogous to membrane time constants) is important, as these time constants affect synchronization frequency 49 and enable neurons with a greater diversity of synapses. 115 As discussed in Sec. I, power-law dynamics are necessary for information integration and self-organized criticality, and a power-law frequency distribution can be achieved through the superposition of exponential decay functions with a diversity of

FIG. 7. Dendritic processing with loops. Schematic of two-level loop hierarchy for nonlinear electrical response.

time constants.<sup>30</sup> To achieve this with the dendritic processors shown in Fig. 7, resistors are placed in each DI loop. The L/rtime constant of each DI loop will set its temporal response, and in this way, different dendrites can be given different time constants. Similarly, a resistor can be placed in each SI loop so that each synaptic excitation has a characteristic time constant, as discussed previously. These resistors will also accomplish the task of purging flux from the SI and DI loops to avoid saturation. As indicated in Fig. 7, inhibition can be applied at various points in the loop hierarchy, including specific synaptic loops, dendritic loops, the neuronal loop, and even the current source to the light emitter. These different structural implementations of inhibition are analogous to the three main forms of inhibition observed in biological neurons, wherein interneurons target dendrites, the soma, and the axon initial segment.<sup>5</sup>

## D. Discussion regarding synaptic receiver circuits

The present section has investigated a superconducting optoelectronic neuron receiver circuit utilizing an analog photon-to-fluxon transducer, based on an SPD in parallel with a JJ, that couples flux to a storage loop. The synaptic weight can be enacted by changing the bias to the JJ. One thousand of these synapses can be inductively coupled to an integration loop and ultimately to a thresholding JJ. Designs for single-photon-sensitive receivers capable of operating on rate-coded signals as well as two-photon-sensitive receivers capable of operating on temporally coded signals have been discussed. Excitatory as well as inhibitory behavior has been simulated, and a hierarchy of loops for dendritic processing has been proposed.

An important area of future investigation regards the resilience of the proposed circuits to flux noise. There are several reasons why flux noise is less likely to be problematic in this context than in superconducting digital circuits or superconducting qubits. First, loop neurons are likely to utilize flux-storage loops with large inductance, and thermal current noise scales as  $L^{-1/2}$ . Second, during a synaptic firing event, tens to hundreds of flux quanta are generated. Therefore, thermal fluctuations that result in the production of order one flux quantum at a synaptic firing junction are of little consequence. This form of noise will lead to a reduction in the resolution of synaptic weights (reduced synaptic bit depth), but will otherwise maintain viability. Third, this form of information processing is classical, so issues related to noise in the phase of the superconducting wave function that are relevant to superconducting qubits are not pertinent to loop neurons. Fourth, many of the loops used in these computational circuits have L/r leak rates by design. Flux that may be trapped in loops during initial cooling will be dissipated rapidly. The synaptic storage loops (to be discussed in Sec. III) are intended to store memories without leak, and, therefore, these loops may be susceptible to unwanted flux trapping. However, even this effect may not be problematic, resulting only in a statistical distribution of initial synaptic weights. The plasticity mechanisms to be discussed next will adapt the network's synapses to a functional operating point. Nevertheless, these qualitative arguments regarding resilience to noise require more rigorous theoretical and experimental investigation, which will be the subject of future work.

In Sec. I, we argue that cognitive systems benefit from information integration across spatial and temporal scales. Temporal integration is achieved with a power-law distribution of neural oscillation frequencies. The receiver circuits presented in this work enable this functionality in at least two ways. First, they are fast and can detect photon communication events at 20 MHz and possibly faster. The brain oscillates at frequencies from 0.05 Hz to 600 Hz. We assume that loop neurons can oscillate from 1 Hz to 20 MHz, and the actual range may be larger. While the human brain oscillates at frequencies spanning 4 orders of magnitude, these receivers could contribute to oscillations across 7 orders of magnitude or more, indicating potential for information integration across very large networks<sup>28</sup> (see Sec. V C 3). The second manner in which these receivers are well suited to achieving a power-law frequency distribution is that their oscillatory response is tunable, so each neuron can participate in a broad range of oscillations. This tunable response is achievable by changing synaptic weights as well as the threshold of the JJ in the NR loop or DR loops via bias currents. Tunability also results from changing which synapses are effective at a given time using inhibition and dendritic processing. Such dynamic effects in synapses and neurons in the brain are crucial for maximally utilizing the time domain for information integration. <sup>18</sup>

Finally, we point out that while the circuits presented here utilize photons for communication and to trigger synaptic firing events, similar functionality is achievable using only fluxons. The SPD in Fig. 2(b) can be replaced by a JJ. The same techniques of utilizing a hierarchy of integration loops, dendritic processing, and synaptic weighting can be used in those circuits as well. Achieving the communication necessary for large networks 107 will be cumbersome with purely electronic circuits. Yet, such neurons may fire at rates beyond 10 GHz with very low power consumption when driving up to ≈20 synaptic connections. Networks combining electronic and optoelectronic neurons extend the power-law degree distribution to lower degree and the power-law frequency distribution to higher frequency. Purely electronic, JJ-based neurons and synapses have been proposed 108,116,117 and demonstrated. 118,1 We point out how the circuits presented here can be converted to purely electrical neurons to illustrate the continuity of electronic and photonic implementations and to show that networks with both electrical and optical neurons working in conjunction based on the same neural principles and fabrication process can be achieved.

## III. SYNAPTIC PLASTICITY

The synaptic weights between nodes of a neural system are crucial memory elements that affect dynamics and computation.  $^{18,51,80,81}$  In the loop neurons under consideration, the photon-to-fluxon transduction that occurs during a synaptic firing event is implemented with an SPD in parallel with a JJ, as described in Sec. II. To change the number of fluxons generated during the synaptic firing event, one can simply change the current bias across  $J_{\rm sf}$ . The circuits presented in this section are designed to dynamically modify the current bias  $I_{\rm sy}$  to  $J_{\rm sf}$  (see Fig. 2). We refer to the circuits that modify  $I_{\rm sy}$  as synaptic update circuits.

In general, there will be a chosen weakest synaptic strength and strongest synaptic strength at each synapse, and in general, the weakest synaptic strength may be achieved with  $I_{\rm sy}^{\rm min}>0$ . Thus, it is the goal of a synaptic update circuit to vary  $I_{\rm sy}$  over some range  $I_{\rm sy}^{\rm min}\leq I_{\rm sy}\leq I_{\rm sy}^{\rm max}$ . In certain contexts, it is sufficient for  $I_{\rm sy}$  to only be able to take two values,  $I_{\rm sy}^{\rm 120}$  while in other learning environments, it may be advantageous to access many values of  $I_{\rm sy}$  between  $I_{\rm sy}^{\rm min}$  and  $I_{\rm sy}^{\rm max}$ . In Sec. II, we identified  $I_{\rm sy}^{\rm min}=1\,\mu{\rm A}$  and  $I_{\rm sy}^{\rm max}=3\,\mu{\rm A}$ .

The circuits described in this section modify  $I_{\rm sy}$  in either a supervised manner using JJs or an unsupervised manner using SPDs in conjunction with JJs. For supervised operation, controlled inputs are presented to the system, and the system provides an output. The output from the system is compared to a desired output, and an error is calculated based on a cost function. This error is then used to update the configuration of the system, often through backpropagation. The objective of supervised learning is usually to train the hardware to perform a specific task.  $^{122}$

For larger neural systems performing general cognitive functions, it is advantageous to operate in an unsupervised manner. Unsupervised learning often refers to the process of learning to categorize unlabeled data. Here, we use the term in a more general sense to refer to systems that learn without any supervisory control. In this modality, no outside entity modifies synaptic weights. Such an approach to learning is scalable in that a user is not required to calculate or adjust the network parameters, so systems with many degrees of freedom can be realized. Unsupervised learning requires that internal activity of the network be capable of adjusting the degrees of freedom to form a useful representation of the information it is expected to process. This operation is achieved through a variety of activity-based plasticity mechanisms, including spike-timing-dependent plasticity (STDP).

For either supervised of unsupervised learning, the memory update signals add or remove flux from a storage loop, which is inductively coupled to  $I_{sy}$ . This loop is referred to as the synaptic storage (SS) loop, and the flux stored in this loop functions as the memory for the synapse.

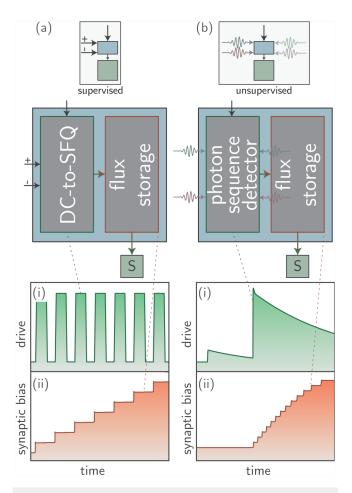

FIG. 8. (a) Supervised synaptic weights. The top box references the schematic of Fig. 1, and summary of operation is shown below. For supervised learning, input square pulses add or remove fluxons from a loop, which strengthens or weakens the synaptic weight. (b) Synaptic update in unsupervised mode. Photons from pre- and postsynaptic neurons update the weight by changing the flux in the SB loop.

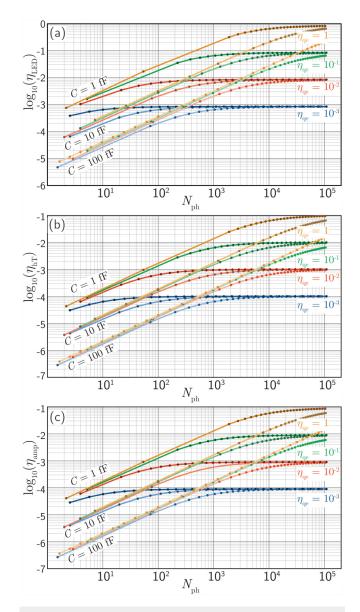

For large-scale cognitive computing, we are interested in systems that will interact continuously with their environment, be capable of immediately assimilating new information, and also capable of remembering events as long as possible. Such competing memory demands are sometimes referred to as the adaptability-precision trade-off, and the best-performing synapses in this regard are complex<sup>54</sup> and may have many stable levels.<sup>55</sup> In human subjects, memories have been observed to fade with a power-law temporal dependence. 123,124 It is difficult to do better than power-law forgetting with plastic synapses that continually adapt,<sup>54</sup> and simple synapses lose their memory trace most quickly.<sup>55</sup> Here, we show synapses with a number of stable states ranging from two to hundreds. These synapses have dynamically variable memory update rates, making the synapses suitable for power-law memory retention.

The circuits implemented to control  $I_{sy}$  must meet several criteria: (1) transition between the minimum and maximum values of  $I_{sy}$  should be possible with a specified number of increments to control the learning rate; (2) the circuit should not be able to set  $I_{sv}$  outside of this range so that simple update rules or training algorithms do not result in excessively large synaptic weights; (3) it should be possible to cycle the value of  $I_{sv}$  from minimum to maximum and back repeatedly without degradation; (4) in addition to a means by which the synaptic weights can be incremented by an external supervisor, there should be a means by which correlated photon signals from the two neurons associated with a synapse can strengthen or weaken the synaptic weight depending on the relative arrival times of the signals from the two neurons; (5) within this unsupervised mode of operation, synaptic update events should be induced by single-photon signals to fully exploit the energy efficiency of superconducting optoelectronic hardware; and (6) the transition probability between synaptic states should also be dynamically adjustable based on photonic signals to achieve metaplastic behavior. This section explores circuit designs satisfying these criteria.

Qualitative explanation of the memory update process is shown in Fig. 8(a) for supervised learning and in Fig. 8(b) for unsupervised learning. For the simplest supervised binary synapse, a flux-quantum memory cell can be used to switch between the strong and weak synaptic states in 50 ps. This binary design can be extended to a multistable synapse that can modify the synaptic weight between the fully potentiated and fully depressed states with hundreds of stable intermediate levels, and implementations with more or less resolution are straightforward to achieve. For unsupervised learning, we consider a circuit that can implement a Hebbian learning rule that potentiates a synaptic connection using one photon from the presynaptic neuron and one photon from the postsynaptic neuron. We generalize this circuit to implement full STDP wherein a synaptic weight can be either potentiated or depressed based on timing correlations. This STDP circuit uses single-photon signals at four ports. Implementations of short-term plasticity, homeostatic plasticity, and metaplasticity are also possible. By combining these synaptic update circuits, it is possible to realize neurons with a distribution of synapses that update at different rates as well as ensembles of neurons wherein different neurons store information about different stimuli learned at different times, thus achieving a network with rapid adaptability and long memory retention times necessary for cognition.

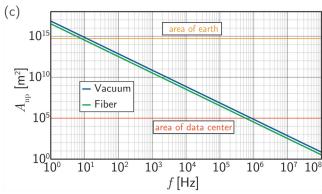

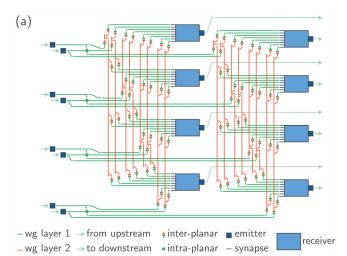

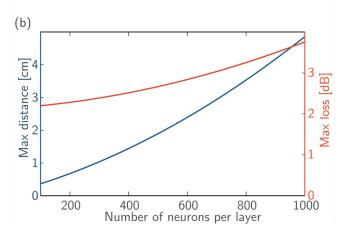

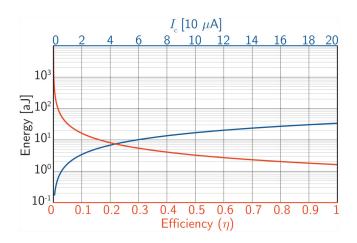

## A. Supervised learning